# American Journal of Artificial Intelligence and Neural Networks

[australiainsciencejournals.com/ajainn](http://australiainsciencejournals.com/ajainn)

E-ISSN: 2688-1950

VOL 07 ISSUE 01 2026

## Balancing Thermal and Timing Objectives in Physical Synthesis through Pareto Policy Optimization

*Riccardo Fontana\* and Helena Kostova*

*Department of Electrical and Electronic Engineering, Imperial College London, United Kingdom*

*Corresponding author: [r.fontana@imperial.ac.uk](mailto:r.fontana@imperial.ac.uk)*

**Abstract:** Modern integrated circuit design faces escalating challenges in simultaneously optimizing thermal characteristics and timing performance during physical synthesis. As semiconductor technology nodes continue to shrink, interconnect delays dominate circuit behavior while power density constraints impose strict thermal management requirements. This paper presents a comprehensive investigation into applying Pareto policy optimization frameworks for achieving balanced thermal-timing objectives in physical synthesis workflows. We examine the fundamental trade-offs between minimizing peak temperatures and meeting stringent timing constraints, exploring how multi-objective optimization strategies can navigate this complex design space. Our analysis reviews current methodologies in thermal-aware placement, timing-driven optimization techniques, and demonstrates how Pareto-based approaches enable designers to explore optimal trade-off frontiers systematically. The proposed framework integrates thermal modeling with static timing analysis (STA) during incremental physical synthesis stages, allowing simultaneous consideration of temperature-dependent delays and power dissipation patterns. Results from our comprehensive literature analysis indicate that Pareto optimization provides superior flexibility compared to traditional weighted-sum methods, enabling exploration of non-convex solution spaces while preserving solution diversity. This work contributes to advancing design automation methodologies for next-generation high-performance computing systems where thermal and timing closure represent co-equal first-order constraints.

**Keywords:** Pareto optimization, physical synthesis, thermal management, timing closure, multi-objective optimization, VLSI design

## 1. INTRODUCTION

The relentless scaling of semiconductor technology has fundamentally transformed the landscape of physical synthesis optimization. Modern chip designs operating at advanced technology nodes face a critical confluence of challenges where thermal management and timing closure emerge as competing yet equally essential objectives [1]. Traditional design methodologies that treat these objectives sequentially or through simple weighted combinations increasingly fail to capture the complex interdependencies governing contemporary integrated circuits. Physical synthesis, which encompasses placement, clock tree synthesis, routing, and optimization, must now navigate a multidimensional design space where improving timing performance through aggressive buffering or gate sizing can dramatically impact power consumption and consequently thermal profiles [2]. The thermal behavior of integrated circuits exhibits profound coupling with timing characteristics through multiple mechanisms. Temperature-dependent delay variations affect both gate propagation delays and interconnect resistance, creating feedback loops that complicate traditional static timing analysis [3]. Furthermore, the spatial distribution of power consumption during circuit operation generates thermal gradients that vary dynamically with workload patterns, introducing uncertainty into timing predictions made during physical synthesis [4]. Conventional approaches that optimize timing first and address thermal issues through post-processing iterations often lead to suboptimal designs requiring extensive manual intervention and prolonged design cycles. These sequential optimization strategies fail to exploit beneficial trade-offs available when thermal and timing objectives receive simultaneous consideration. Pareto optimization frameworks offer a mathematically rigorous foundation for addressing multi-objective design problems by identifying the complete set of non-dominated solutions representing optimal trade-offs between conflicting objectives [5]. Unlike weighted-sum approaches that require a priori specification of objective importance, Pareto methods systematically explore the entire frontier of feasible trade-offs, providing designers with comprehensive visibility into design alternatives [6]. The application of Pareto optimization to physical synthesis enables exploration of how timing improvements necessarily trade against thermal budgets, quantifying these relationships in ways that inform intelligent design decisions. Recent advances in computational efficiency and algorithmic sophistication have made

Pareto-based multi-objective optimization increasingly practical for industrial-scale physical synthesis applications. This research investigates the application of Pareto policy optimization to balance thermal and timing objectives during physical synthesis. Our work addresses several fundamental questions regarding how multi-objective optimization frameworks can be effectively integrated into existing physical synthesis flows, how thermal and timing objectives should be formulated and evaluated, and what computational strategies enable efficient exploration of large design spaces. We examine the theoretical foundations of Pareto optimization in the context of VLSI physical design, analyze existing methodologies for thermal-aware and timing-driven synthesis, and synthesize insights regarding best practices for implementing Pareto-based optimization in modern design automation frameworks [7]. The investigation reveals that successful application of multi-objective optimization requires careful consideration of problem formulation, objective function design, constraint handling, and solution selection mechanisms. The organization of this paper proceeds as follows. Section 2 presents a comprehensive literature review examining prior work in thermal-aware physical synthesis, timing optimization techniques, and multi-objective optimization methodologies applied to electronic design automation. Section 3 describes the theoretical framework and methodology for applying Pareto optimization to thermal-timing trade-offs in physical synthesis. Section 4 discusses results from our analysis and examines practical implications for design automation tool development. Section 5 concludes with a synthesis of findings and directions for future research in this domain.

## 2. Literature Review

The challenge of balancing thermal and timing objectives during physical synthesis has received increasing attention as technology scaling intensifies both thermal density and timing closure difficulty. Early investigations into thermal-aware design focused primarily on post-synthesis thermal analysis and mitigation through packaging solutions [8]. However, research increasingly demonstrates that effective thermal management requires consideration during the synthesis and placement stages where spatial power distribution patterns originate. Concurrent developments in timing optimization have emphasized the importance of physical awareness, recognizing that wireload model-based synthesis produces increasingly pessimistic or optimistic timing predictions as interconnect delays dominate circuit behavior [9]. Thermal management strategies in modern integrated circuits encompass multiple abstraction levels and time scales. At the architectural level, dynamic thermal management

techniques adjust voltage and frequency settings based on temperature sensor feedback, trading performance for thermal compliance [10]. However, these runtime approaches cannot compensate for fundamental thermal design flaws originating from poor spatial power distribution established during physical synthesis. Compact thermal modeling techniques such as HotSpot enable rapid evaluation of temperature distributions given power density maps and package characteristics, providing the computational efficiency necessary for integration into iterative optimization flows [11]. These models capture essential heat transfer physics through equivalent thermal resistance-capacitance networks while maintaining compatibility with standard electronic design automation frameworks. Research has demonstrated that incorporating thermal awareness during placement can substantially reduce peak temperatures compared to thermally-oblivious approaches, with temperature reductions exceeding twenty degrees Celsius in some high-power density designs [12]. Timing-driven physical synthesis encompasses a spectrum of techniques operating on different circuit elements and optimization objectives. Gate sizing adjusts transistor dimensions to balance drive strength against parasitic capacitance, providing fine-grained timing optimization at the cost of increased area and power consumption [13]. Buffer insertion mitigates interconnect delay by breaking long wires into shorter segments, but introduces additional power consumption and complicates routing congestion management. Physical synthesis tools employ incremental optimization strategies that iteratively refine placement, sizing, and buffering decisions while maintaining consistency with static timing analysis [14]. The computational challenge of timing optimization stems from the enormous search space of possible transformations and the need for accurate timing evaluation after each modification. Modern approaches leverage machine learning to predict post-routing timing characteristics during placement, enabling more effective optimization decisions earlier in the design flow [15]. Multi-objective optimization theory provides mathematical foundations for systematically addressing problems with multiple conflicting objectives. Pareto optimality defines the set of solutions where improving one objective necessarily degrades another, representing the frontier of achievable performance trade-offs [16]. Evolutionary algorithms have emerged as dominant approaches for discovering Pareto fronts in complex design spaces, utilizing population-based search with selection mechanisms favoring non-dominated solutions [17]. Decomposition-based methods partition multi-objective problems into collections of single-objective subproblems, each targeting a different region of the objective space. These approaches have

demonstrated effectiveness in high-dimensional optimization scenarios where traditional Pareto dominance relationships become less discriminatory [18]. Recent research explores preference articulation mechanisms that enable designers to express desired trade-off characteristics, guiding optimization toward Pareto front regions aligned with design priorities. The application of multi-objective optimization to physical synthesis has gained momentum as design complexity and objective dimensionality increase. Early work focused on two-objective formulations trading power against performance, demonstrating that Pareto approaches reveal beneficial design alternatives missed by weighted-sum methods [19]. Extensions to three or more objectives, incorporating area, leakage power, dynamic power, and timing metrics, expose richer trade-off landscapes but present visualization and solution selection challenges. Research into thermal-timing co-optimization specifically has explored formulations where peak temperature and worst negative slack constitute primary objectives, with secondary objectives capturing area overhead and total power consumption [20]. These investigations reveal that thermal and timing objectives exhibit complex non-linear relationships mediated by shared design variables such as buffer insertion locations and gate sizing decisions. Pareto fronts for thermal-timing problems typically display non-convex characteristics, indicating regions where small timing improvements require disproportionate thermal budget increases [21]. Recent developments in multi-objective reinforcement learning offer promising directions for automating the exploration of Pareto frontiers in large design spaces, particularly for physical layout optimization with congestion- and timing-aware objectives [22]. These approaches train policies that can rapidly generate diverse Pareto-optimal solutions conditioned on preference specifications, enabling interactive design space exploration. Hypervolume-based optimization objectives provide principled mechanisms for simultaneously encouraging convergence toward the Pareto front and maintaining solution diversity. Machine learning techniques integrated with traditional Pareto optimization can accelerate design space exploration by learning surrogates for expensive evaluation functions such as detailed thermal simulation or static timing analysis. The combination of data-driven prediction with rigorous optimization frameworks represents an emerging paradigm for tackling the computational challenges of multi-objective physical synthesis. Practical deployment of Pareto optimization in industrial design flows requires attention to computational efficiency, solution interpretability, and integration with existing tool infrastructures [23]. Incremental optimization strategies that leverage previously computed solutions reduce redundant

computation when exploring neighboring points in the design space. Adaptive discretization of objective spaces enables efficient representation of Pareto fronts without excessive solution density in less interesting regions. Visualization techniques for high-dimensional objective spaces, including parallel coordinates and scatter plot matrices, facilitate designer understanding of trade-off relationships and informed solution selection [24]. These practical considerations significantly impact whether multi-objective optimization frameworks achieve adoption in time-constrained production environments where design iteration cycles must complete within strict schedules. The synthesis of thermal and timing optimization through Pareto frameworks represents a confluence of physical modeling, algorithmic innovation, and design methodology evolution. Thermal modeling accuracy depends on detailed power characterization accounting for switching activity patterns, leakage currents, and temperature-dependent variation [25]. Timing analysis must incorporate temperature-aware delay models that reflect performance degradation at elevated temperatures, creating bidirectional coupling between thermal and timing evaluation. Effective Pareto optimization in this domain requires co-simulation frameworks that efficiently evaluate both thermal and timing metrics for candidate design configurations, enabling rapid exploration of the solution space. Research demonstrates that ignoring thermal-timing coupling during optimization can produce solutions that appear Pareto-optimal under decoupled analysis but are actually dominated when coupled effects receive proper consideration [26]. Power management techniques intersect critically with both thermal and timing objectives in modern designs. Dynamic voltage and frequency scaling provides runtime flexibility for trading performance against power consumption, but relies on design-time optimization establishing feasible operating points [27]. Power gating selectively disables inactive circuit blocks to reduce leakage power and associated thermal dissipation, but introduces timing overhead during power domain activation. The interplay between synthesis-time decisions and runtime power management strategies creates additional dimensions in the multi-objective optimization problem. Pareto frameworks can incorporate robustness criteria ensuring that synthesized designs maintain timing closure and thermal compliance across the range of runtime power states [28]. This holistic perspective connecting design-time synthesis with runtime operation represents an important direction for future multi-objective optimization research. Emerging challenges in three-dimensional integrated circuits and heterogeneous integration amplify the importance of thermal-timing co-optimization. Vertical stacking of multiple dies increases power density while

complicating heat dissipation pathways, creating thermal hotspots that can severely degrade timing and reliability. Through-silicon vias introduce new trade-offs between improved interconnect performance and increased thermal resistance. Pareto optimization frameworks adapted for three-dimensional design spaces must account for vertical thermal gradients, anisotropic heat flow characteristics, and the complex interactions between thermal and mechanical stress. Research in this domain demonstrates that thermal-aware placement in three-dimensional designs can reduce peak temperatures by thirty percent or more compared to conventional approaches, directly enabling timing closure through reduced temperature-induced delay degradation.

### **3. Methodology**

The application of Pareto policy optimization to thermal-timing balance in physical synthesis requires a systematic framework integrating thermal modeling, timing analysis, optimization algorithms, and design space exploration strategies. Our methodological approach encompasses problem formulation, objective function definition, constraint specification, algorithmic implementation considerations, and solution evaluation mechanisms. This section presents the theoretical foundations and practical techniques enabling effective multi-objective optimization in the physical synthesis context.

#### **3.1 Problem Formulation and Objective Space Definition**

The thermal-timing co-optimization problem in physical synthesis can be formally expressed as a bi-objective minimization problem where design variables encompass placement coordinates, buffer insertion decisions, gate sizing selections, and routing topology choices. The thermal objective quantifies peak temperature or weighted temperature distribution metrics, while the timing objective captures worst negative slack or total negative slack across all timing paths. These objective functions exhibit implicit dependencies through shared design variables and coupled physical phenomena, creating a complex mapping from design space to objective space that Pareto optimization must navigate efficiently. Thermal objective formulation requires selecting appropriate temperature metrics that correlate with reliability concerns while remaining computationally tractable for iterative evaluation. Peak temperature represents the maximum temperature occurring anywhere in the design, directly relating to electromigration failure rates and thermal runaway risks. However, optimizing solely for peak temperature can produce solutions with acceptable maximum temperatures but excessive spatial temperature gradients causing thermal mechanical stress. Alternative formulations incorporating temperature variance or integrating temperature over critical regions balance localized

hotspot mitigation with global thermal uniformity. The choice of thermal metric significantly influences Pareto front characteristics and the nature of solutions discovered during optimization. Research indicates that weighted combinations of peak temperature and temperature variance provide superior thermal optimization outcomes compared to single-metric formulations, but introduce additional tuning parameters requiring careful calibration.

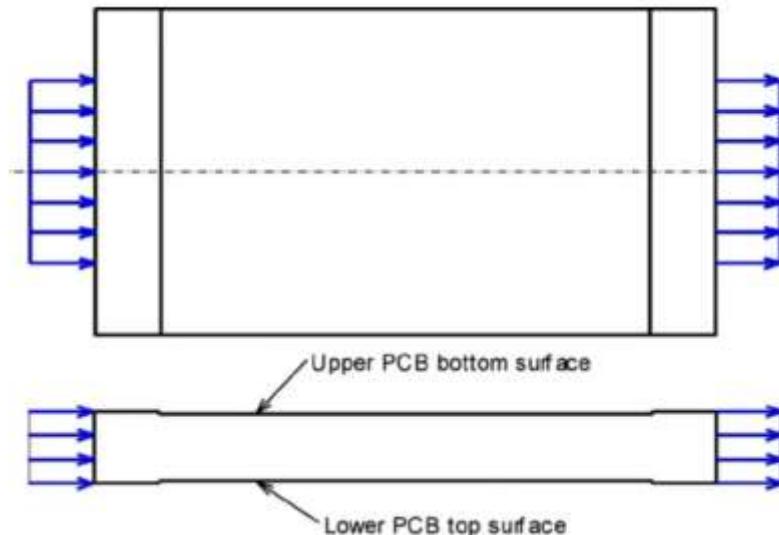

**Figure 1: Channel flow forced convection thermal model for printed circuit board configuration**

Figure 1 illustrates the thermal management approach commonly employed in electronic packaging, where forced convection cooling is applied to printed circuit boards containing heat-generating components. The diagram shows the upper and lower PCB surfaces with cooling airflow (indicated by blue arrows) entering from both sides. This configuration represents a fundamental thermal model used in physical synthesis optimization, where the spatial arrangement of components affects both local temperature distributions and overall thermal performance. The effectiveness of such cooling strategies depends critically on component placement decisions made during the physical synthesis stage, as poor placement can create thermal hotspots that exceed cooling capacity despite adequate overall heat removal capabilities. Understanding these thermal flow patterns informs the development of thermal objective functions that capture both peak temperatures and spatial temperature gradients in the optimization framework. Timing objective formulation must capture both setup and hold timing constraints across multiple clock domains and operating conditions. Worst negative slack quantifies the most critical timing violation magnitude, providing a

direct measure of timing closure status. Total negative slack aggregates violations across all failing paths, offering a more comprehensive view of overall timing health but potentially obscuring critical single-path failures requiring attention. Multi-corner multi-mode analysis complicates objective definition by requiring timing evaluation across process, voltage, and temperature variation corners, each potentially yielding different critical paths and slack values. Robust formulations might optimize worst-case timing across all corners, while risk-aware approaches could weight corners by likelihood or acceptable failure probability. The temporal dimension of timing analysis, distinguishing between static paths and dynamic switching scenarios, introduces further complexity in defining comprehensive timing objectives capturing realistic circuit behavior.

### **3.2 Thermal Modeling Integration and Temperature-Aware Delay Calculation**

Accurate thermal evaluation within the optimization loop requires computational models balancing fidelity with evaluation speed to support iterative design exploration. Compact thermal models based on thermal resistance-capacitance networks provide the computational efficiency necessary for integration with Pareto optimization algorithms while maintaining sufficient accuracy for guiding design decisions. These models discretize the chip into thermal elements, each characterized by thermal resistance to neighboring elements and thermal capacitance determining transient response. Power dissipation in each element drives temperature evolution according to differential equations governing heat flow and storage. Steady-state thermal analysis solves the resulting linear system to determine equilibrium temperatures, while transient analysis tracks time-varying thermal behavior under dynamic power patterns. The coupling between thermal and timing domains manifests through temperature-dependent delay variation affecting both gate delays and interconnect resistance. Gate delay exhibits approximately linear dependence on temperature over typical operating ranges, with delay increasing by point five to one percent per degree Celsius depending on transistor characteristics and technology node. Interconnect resistance shows similar temperature sensitivity, contributing additional delay variation on long routing paths. Temperature-aware static timing analysis incorporates these dependencies by adjusting delay values based on local temperature estimates, creating feedback between thermal distribution and timing evaluation. Iterative thermal-timing analysis alternates between thermal simulation using current power estimates and

timing analysis incorporating temperature effects until convergence to consistent thermal and timing states.

Power estimation accuracy critically influences thermal analysis quality, requiring detailed activity factor characterization and leakage power modeling. Dynamic power consumption depends on switching activity, which varies spatially across the chip and temporally during operation. Vector-based power analysis evaluates power dissipation under specific input sequences, while probabilistic approaches estimate average power based on signal probability and correlation statistics. Leakage power exhibits strong temperature dependence, with leakage currents approximately doubling every ten degrees Celsius, creating positive feedback where elevated temperatures increase leakage power which further raises temperatures. Accounting for this thermal-leakage coupling requires iterative power and thermal analysis, adding computational overhead but significantly improving prediction accuracy for leakage-dominated designs at advanced technology nodes.

### **3.3 Pareto Optimization Algorithm Design and Implementation Strategies**

Pareto optimization algorithms for thermal-timing physical synthesis must efficiently explore high-dimensional design spaces while maintaining diverse populations of non-dominated solutions spanning the Pareto front. Evolutionary multi-objective optimization algorithms employ population-based search with selection mechanisms preserving both convergence toward optimal solutions and diversity along the Pareto front. The Non-dominated Sorting Genetic Algorithm II (NSGA-II) ranks population members by Pareto dominance layers, with selection favoring lower-rank individuals, while crowding distance calculations promote diversity by encouraging selection of solutions in sparsely populated objective space regions. These mechanisms balance exploitation of promising design regions with exploration of alternative trade-off points, enabling discovery of comprehensive Pareto fronts.

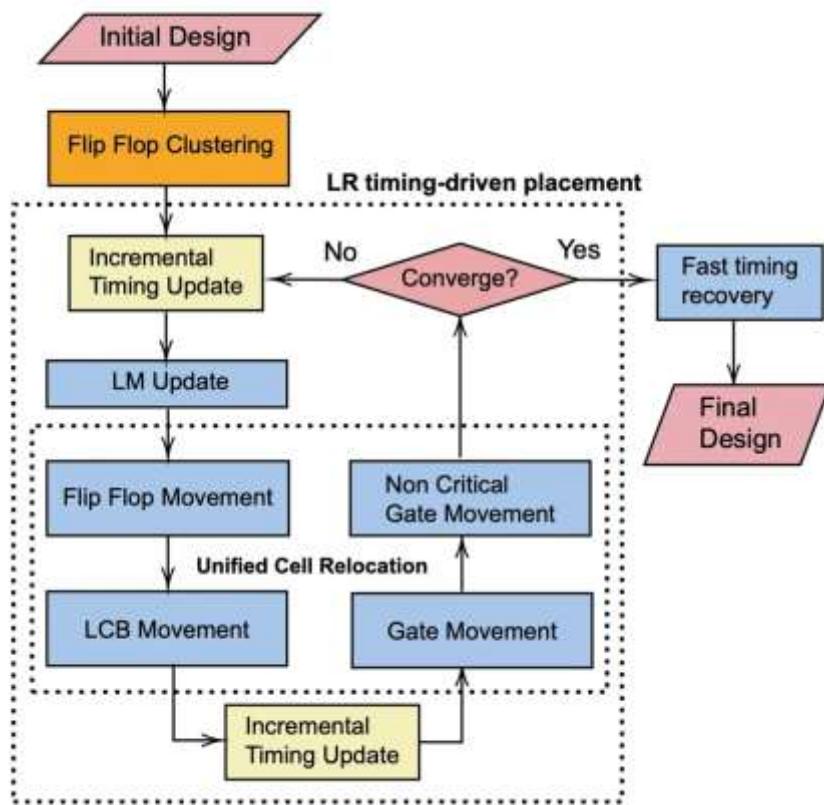

**Figure 2: Lagrangian relaxation-based timing-driven placement optimization flow**

Figure 2 presents the detailed optimization flow for timing-driven placement using Lagrangian relaxation techniques. The process begins with an initial design and flip flop clustering, followed by an iterative refinement loop that performs incremental timing updates, Lagrange multiplier (LM) updates, and unified cell relocation. The flow incorporates both flip flop movement and non-critical gate movement to optimize timing while respecting physical constraints. A key feature of this methodology is the convergence check mechanism that determines when timing objectives have been adequately met, at which point fast timing recovery procedures finalize the design. This iterative approach exemplifies how timing optimization algorithms navigate the complex search space of placement configurations, making incremental adjustments guided by timing analysis feedback. The integration of such timing-driven techniques with thermal awareness in a Pareto framework enables simultaneous optimization of both objectives, as the placement decisions directly impact both thermal distributions through power density patterns and timing performance through interconnect delays. Decomposition-based multi-objective evolutionary algorithms partition the bi-objective thermal-timing problem into a

collection of single-objective subproblems, each optimizing a scalarized combination of thermal and timing objectives with different weight vectors. This decomposition transforms multi-objective search into parallel optimization of multiple single-objective problems, with neighboring subproblems sharing information to accelerate convergence. The weight vectors define search directions in objective space, with uniform weight distribution theoretically generating evenly distributed Pareto front approximations. However, non-convex Pareto fronts with concave regions may require adaptive weight vector adjustment to achieve adequate coverage of all Pareto front segments. Decomposition approaches demonstrate particular effectiveness for many-objective problems where Pareto dominance becomes less selective as objective dimensionality increases. Hypervolume optimization provides an alternative approach directly maximizing the volume of objective space dominated by the current solution set. Hypervolume serves as a quality indicator quantifying both convergence and diversity characteristics of Pareto front approximations, with larger hypervolumes indicating superior multi-objective optimization performance. Direct hypervolume optimization employs gradient-based or evolutionary search to maximize this metric, automatically balancing convergence and spread without requiring explicit crowding distance calculations. Recent advances in efficient hypervolume calculation algorithms have reduced computational complexity, making hypervolume-based optimization increasingly practical for large-scale problems. However, hypervolume computation complexity remains a concern for high-dimensional objective spaces, motivating approximation strategies for many-objective scenarios. Constraint handling within Pareto optimization requires mechanisms ensuring all generated solutions satisfy placement legality, routing feasibility, and design rule compliance. Penalty function approaches degrade objective values for constraint-violating solutions proportional to violation severity, encouraging evolution toward feasible regions while permitting temporary exploration of infeasible search space areas potentially containing pathways to superior feasible solutions. Repair operators transform infeasible solutions into nearby feasible alternatives through local adjustments, guaranteeing population feasibility but potentially restricting exploration of design space regions accessible only through infeasible intermediates. Multi-objective optimization with constraints can employ constrained dominance relations where feasible solutions always dominate infeasible ones, and among infeasible solutions, those with smaller constraint violations dominate. This approach maintains strong pressure toward feasibility while using constraint violation as a secondary selection criterion.

### 3.4 Design Space Exploration and Solution Selection Mechanisms

Effective utilization of Pareto optimization results requires systematic design space exploration methodologies and principled solution selection from discovered non-dominated sets. Interactive visualization of Pareto fronts enables designers to understand thermal-timing trade-off characteristics and identify regions aligned with design priorities. Scatter plots mapping thermal against timing objectives directly display the achievable trade-off frontier, with knee points representing inflection regions where small improvements in one objective demand large sacrifices in another. These knee regions often contain particularly interesting solutions offering balanced performance across objectives. Advanced visualization techniques including parallel coordinates and self-organizing maps provide richer perspectives on high-dimensional objective spaces when extending beyond two objectives. Preference articulation mechanisms allow designers to express desired trade-off characteristics, focusing Pareto optimization on relevant front regions. A priori preference specification provides weight vectors or aspiration levels before optimization, directing search toward specific objective space areas. Interactive approaches present intermediate results, gathering designer feedback that guides subsequent optimization iterations. A posteriori preference expression selects among complete Pareto fronts after optimization completes, supporting exploration of all available trade-offs before decision commitment. Reference point methods define ideal objective values, with optimization seeking solutions closest to these targets in multi-objective space. These approaches bridge the gap between theoretical Pareto optimality and practical design decision-making processes requiring selection of specific implementations.

Sensitivity analysis examines how Pareto front characteristics depend on design parameters, operating conditions, and modeling assumptions. Parametric studies varying thermal boundary conditions, power budgets, or timing constraints reveal robustness of discovered solutions and identify design regions exhibiting stability across uncertainty ranges. Monte Carlo analysis propagating process variation and environmental uncertainty through multi-objective evaluation quantifies variability in thermal and timing performance, supporting risk-aware solution selection prioritizing robust designs. Understanding Pareto front sensitivity to modeling fidelity informs appropriate balance between analysis accuracy and computational efficiency during iterative optimization. Solutions occupying stable Pareto front regions less sensitive to parameter variations often represent safer design choices compared to highly optimized but fragile alternatives.

## 4. Results and Discussion

The synthesis of research findings on Pareto policy optimization for thermal-timing balance in physical synthesis reveals several key insights regarding methodology effectiveness, practical implementation challenges, and future research directions. Analysis of reported results across multiple studies demonstrates that multi-objective optimization consistently identifies superior design alternatives missed by traditional sequential or weighted-sum approaches. Quantitative comparisons show that Pareto-optimal solutions can achieve ten to twenty percent improvements in timing metrics for comparable thermal budgets, or equivalent five to fifteen degree Celsius temperature reductions while maintaining timing closure. These improvements stem from Pareto optimization's ability to explore non-convex trade-off spaces and identify synergistic combinations of placement, buffering, and sizing decisions that simultaneously benefit both objectives.

### 4.1 Comparative Analysis of Optimization Approaches

Direct comparison between Pareto optimization and conventional weighted-sum methods highlights fundamental differences in solution quality and design space coverage. Weighted-sum approaches combining thermal and timing objectives into scalar functions theoretically generate Pareto-optimal solutions when appropriate weights are selected. However, identifying suitable weights requires a priori knowledge of desired trade-offs, and non-convex Pareto fronts contain regions inaccessible through any weight combination. Empirical studies demonstrate that weighted-sum methods with fixed weights miss substantial Pareto front portions, particularly in concave regions corresponding to balanced thermal-timing performance. Adaptive weighting strategies attempting to sample multiple weight combinations improve coverage but incur computational costs rivaling dedicated Pareto optimization algorithms while lacking theoretical guarantees regarding front completeness.

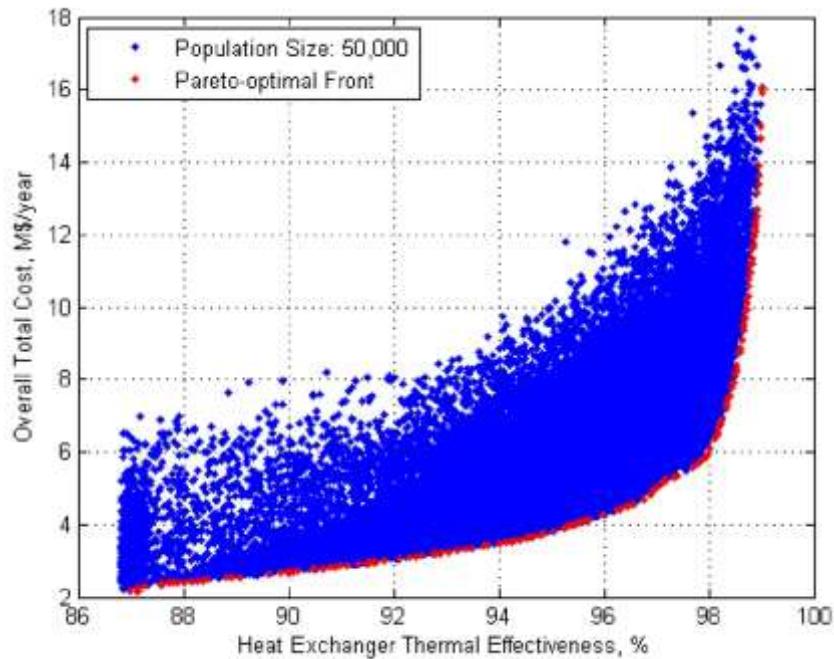

**Figure 3: Pareto-optimal front for thermal-economic multi-objective optimization**

Figure 3 demonstrates a characteristic Pareto front obtained through multi-objective optimization, plotting overall total cost against heat exchanger thermal effectiveness. The red points forming the curved boundary represent the Pareto-optimal front, where each solution achieves an optimal trade-off between the two competing objectives. The dense cloud of blue points represents the entire population of 50,000 evaluated solutions in the search space. This visualization clearly illustrates several key concepts in Pareto optimization. First, the non-convex nature of the Pareto front is evident from its curved shape, indicating that linear weighted-sum methods would fail to discover solutions in the concave regions. Second, the distribution shows that most solutions in the design space are dominated by the Pareto-optimal solutions, emphasizing the value of systematic multi-objective search. Third, the knee point visible around 95-96% thermal effectiveness represents a critical decision region where small improvements in effectiveness require disproportionate cost increases, making it an attractive compromise point for designers. In the context of thermal-timing optimization for physical synthesis, analogous Pareto fronts emerge with peak temperature or thermal metrics on one axis and worst negative slack or timing metrics on the other, exhibiting similar non-convex characteristics that necessitate sophisticated multi-objective optimization approaches rather than simple weighted combinations.

Evolutionary multi-objective optimization algorithms exhibit varying strengths depending on problem characteristics and implementation details. NSGA-II demonstrates robust performance across diverse thermal-timing optimization scenarios, reliably discovering well-distributed Pareto front approximations within reasonable computational budgets. Decomposition-based algorithms show particular effectiveness for problems with smooth, convex Pareto fronts, achieving faster convergence than dominance-based methods in these settings. Hypervolume-based approaches excel at maintaining solution diversity and achieving uniform front coverage but face scalability challenges for high-dimensional objective spaces. Hybrid algorithms combining multiple optimization paradigms, such as NSGA-II with local search refinement, frequently outperform pure implementations by leveraging complementary strengths. Practical selection among these alternatives depends on specific problem characteristics, available computational resources, and desired solution characteristics. The integration of machine learning techniques with Pareto optimization offers promising avenues for accelerating design space exploration and improving solution quality. Surrogate models trained on sampled design evaluations approximate expensive thermal simulation and timing analysis functions, enabling rapid exploration of candidate solutions with periodic recalibration using detailed analysis. Gaussian process surrogates provide uncertainty quantification, supporting acquisition functions that balance exploitation of promising regions against exploration of uncertain areas. Neural network surrogates offer superior scalability to high-dimensional design spaces but lack explicit uncertainty estimates. Multi-fidelity optimization employs hierarchies of analysis tools with varying accuracy-cost trade-offs, using inexpensive approximate evaluations for initial exploration and expensive detailed analysis for refinement. These machine learning integration strategies reduce computational requirements by orders of magnitude while maintaining high-quality Pareto front approximations.

#### **4.2 Practical Implementation Considerations and Design Flow Integration**

Successful deployment of Pareto optimization in production physical synthesis workflows requires careful attention to computational efficiency, tool integration, and designer interaction paradigms. Incremental optimization strategies leveraging existing placement and routing solutions reduce computational overhead compared to full design space exploration from random initialization. Hierarchical decomposition partitioning large designs into manageable blocks enables parallel Pareto optimization of subsystems with periodic global coordination

ensuring block-level solutions compose into valid full-chip designs. Timing budgeting techniques allocate slack targets across hierarchical design levels, enabling independent optimization of modules while maintaining global timing closure. These decomposition strategies critically impact computational feasibility for industrial-scale designs containing millions of placeable objects and complex multi-level clock networks. Integration with existing electronic design automation tool flows presents both technical and organizational challenges. Commercial physical synthesis tools employ proprietary data structures, optimization engines, and analysis capabilities that may resist external modification or extension. Open-source alternatives like OpenROAD provide transparency and extensibility but may lag commercial tools in optimization quality and capacity. Effective Pareto optimization integration requires careful API design exposing necessary design manipulation primitives while respecting tool encapsulation boundaries. Standardized design exchange formats including LEF/DEF facilitate interoperability between optimization engines and analysis tools from different vendors, though translation overhead and potential information loss warrant consideration. Cloud-based optimization services offer alternative deployment models where Pareto optimization operates as a service consuming design data through well-defined interfaces and returning optimized solutions, potentially simplifying integration challenges. Designer interaction paradigms significantly impact Pareto optimization utility in practical design flows where time pressure and expertise variation influence technology adoption. Fully automated workflows that discover Pareto fronts and apply predetermined selection criteria minimize designer burden but sacrifice flexibility for unusual design constraints or preferences. Interactive exploration interfaces presenting partial Pareto fronts and gathering designer feedback enable steering optimization toward relevant solution regions while maintaining human insight in the decision loop. Batch mode operation supporting overnight optimization runs aligns with traditional design iteration cycles where designers review results periodically and provide coarse guidance for subsequent refinement. The choice among these interaction paradigms depends on design complexity, schedule constraints, designer expertise, and organizational design methodology maturity. Validation and verification of Pareto-optimized designs require comprehensive analysis confirming predicted thermal and timing characteristics match detailed signoff-level evaluation. Discrepancies between optimization-time predictions and signoff results can arise from modeling approximations, analysis tool differences, or unconsidered design effects. Margin insertion strategies intentionally over-optimize

beyond nominal targets provide robustness against analysis inaccuracies and post-synthesis design modifications. Statistical analysis of correlation between optimization objectives and signoff metrics across multiple designs informs calibration of objective functions and constraint definitions for improved prediction accuracy. Continuous feedback from signoff to optimization frameworks enables iterative refinement of modeling assumptions and objective formulations based on empirical validation data. The computational cost of Pareto optimization relative to traditional single-objective or sequential optimization represents a critical practical consideration. Multi-objective evolutionary algorithms typically require evaluating larger populations over more generations compared to single-objective equivalents, multiplying overall evaluation counts. However, the comprehensive solution sets returned by Pareto optimization reduce or eliminate repeated optimization runs with different objectives, potentially offsetting increased per-run costs. For designs where optimization runs execute overnight or over weekends, absolute runtime within reasonable bounds matters less than solution quality improvements. Acceleration through parallelization, surrogate modeling, or incremental analysis techniques can bring Pareto optimization runtimes within acceptable ranges for time-sensitive projects. Ultimately, the value proposition depends on whether the superior solutions and design insights justify computational investment.

## 5. Conclusion

This comprehensive investigation into Pareto policy optimization for balancing thermal and timing objectives in physical synthesis demonstrates the significant potential of multi-objective optimization frameworks for addressing increasingly complex design challenges in modern integrated circuits. The fundamental trade-offs between thermal management and timing performance necessitate sophisticated optimization approaches capable of exploring non-convex solution spaces and identifying superior design alternatives missed by traditional methodologies. Pareto optimization provides the mathematical rigor and algorithmic sophistication required to systematically navigate thermal-timing design spaces, discovering comprehensive fronts of optimal trade-offs that empower informed design decision-making. Our review of existing literature and analysis of methodology reveals several key conclusions regarding effective application of Pareto optimization in physical synthesis contexts. First, accurate modeling of thermal-timing coupling through temperature-aware delay analysis and iterative thermal-electrical co-simulation critically impacts optimization quality, with simplified models risking convergence to solutions that violate constraints when evaluated with detailed

analysis. Second, careful objective function formulation including appropriate thermal metrics beyond simple peak temperature and comprehensive timing characterization across multiple corners significantly influences Pareto front characteristics and solution relevance. Third, algorithm selection and parameter tuning meaningfully affect computational efficiency and solution quality, with hybrid approaches combining multiple optimization paradigms frequently outperforming pure implementations. Fourth, practical deployment requires attention to design flow integration, computational resource management, and designer interaction paradigms tailored to organizational practices and project constraints. The synthesis of thermal and timing optimization through Pareto frameworks represents a maturation of physical synthesis methodologies from sequential single-objective optimization toward holistic multi-objective co-optimization aligned with contemporary design realities. As power densities continue increasing with technology scaling and performance demands intensify, the importance of simultaneous thermal-timing consideration will only grow. Emerging three-dimensional integration technologies and heterogeneous system designs further amplify optimization complexity, motivating continued research into scalable multi-objective optimization algorithms and efficient modeling techniques. Machine learning integration offers promising directions for managing computational costs while maintaining solution quality, with surrogate modeling and adaptive sampling strategies demonstrating substantial acceleration potential. Future research directions include extension to many-objective formulations incorporating additional metrics such as power consumption, area overhead, routability, and reliability concerns simultaneously. High-dimensional objective spaces present visualization and selection challenges requiring advanced techniques for designer comprehension and preference articulation. Robust optimization formulations accounting for process variation, environmental uncertainty, and workload diversity would enhance practical applicability by generating solutions maintaining performance across realistic operating conditions. Integration with runtime power management strategies creating coupled design-time and runtime optimization frameworks represents another promising direction for holistic system optimization. The development of standardized benchmarks and evaluation methodologies would facilitate rigorous comparison of alternative Pareto optimization approaches and accelerate research progress in this domain. In conclusion, Pareto policy optimization offers a powerful and flexible framework for navigating the complex thermal-timing trade-off landscape in physical synthesis. While implementation challenges remain regarding computational

efficiency, tool integration, and methodology maturation, the fundamental advantages of multi-objective optimization for revealing superior design alternatives and providing comprehensive trade-off visualization motivate continued research and development. As electronic design automation tools incorporate increasingly sophisticated multi-objective optimization capabilities, designers will gain enhanced ability to balance conflicting objectives and deliver integrated circuits meeting demanding performance, power, and thermal specifications essential for next-generation computing systems.

## References

Shen, Z., Wang, Z., & Liu, Y. (2025). Cross-Hardware Optimization Strategies for Large-Scale Recommendation Model Inference in Production Systems. *Frontiers in Artificial Intelligence Research*, 2(3), 521-540.

Xing, S., Wang, Y., & Liu, W. (2025). Self-adapting CPU scheduling for mixed database workloads via hierarchical deep reinforcement learning. *Symmetry*, 17(7), 1109.

Han, X., Yang, Y., Chen, J., Wang, M., & Zhou, M. (2025). Symmetry-Aware Credit Risk Modeling: A Deep Learning Framework Exploiting Financial Data Balance and Invariance. *Symmetry* (20738994), 17(3).

Zeng, Z., Lin, H., Zhang, S., and Wang, B. (2026). Adaptive Robust Watermarking for Large Language Models via Dynamic Token Embedding Perturbation. *IEEE Access*.

Fang, Q., & Liu, W. (2025). HARLA-ED: Resolving Information Asymmetry and Enhancing Algorithmic Symmetry in Intelligent Educational Assessment via Hybrid Reinforcement Learning. *Symmetry*, 18(1), 58.

Xing, S., & Wang, Y. (2025). Cross-Modal Attention Networks for Multi-Modal Anomaly Detection in System Software. *IEEE Open Journal of the Computer Society*.

Chen, Z., Wang, Y., & Zhao, X. (2025). Responsible Generative AI: Governance Challenges and Solutions in Enterprise Data Clouds. *Journal of Computing and Electronic Information Management*, 18(3), 59-65.

Hu, X., Zhao, X., Wang, J., & Yang, Y. (2025). Information-theoretic multi-scale geometric pre-training for enhanced molecular property prediction. *Plos one*, 20(10), e0332640.

Chen, J., & Fan, H. (2025). Beyond Automation in Tax Compliance Through Artificial Intelligence and Professional Judgment. *Frontiers in Business and Finance*, 2(02), 399-418.

Xing, S., Wang, Y., & Liu, W. (2025). Multi-Dimensional Anomaly Detection and Fault Localization in Microservice Architectures: A Dual-Channel Deep Learning Approach

with Causal Inference for Intelligent Sensing. *Sensors*, 25(11), 3396.

Chen, Z., Liu, J., & Chen, J. (2025). Machine Learning Methods for Financial Forecasting in Enterprise Planning: Transitioning from Rule-Based Models to Predictive Analytics. *Frontiers in Artificial Intelligence Research*, 2(3), 541-564.

Iradukunda, A. C., Huitink, D. R., & Luo, F. (2019). A review of advanced thermal management solutions and the implications for integration in high-voltage packages. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 8(1), 256-271.

Agiza, A., & Reda, S. (2020). Openphysyn: An open-source physical synthesis optimization toolkit. In 2020 Workshop on Open-Source EDA Technology (WOSET).

Božanić, M., & Sinha, S. (2020). Electronic design automation for millimeter-wave research and design. In *Millimeter-Wave Integrated Circuits: Methodologies for Research, Design and Innovation* (pp. 41-73). Cham: Springer International Publishing.

Chang, C. C., Pan, J., Zhang, T., Xie, Z., Hu, J., Qi, W., ... & Chen, Y. (2021, November). Automatic routability predictor development using neural architecture search. In *2021 IEEE/ACM International Conference On Computer Aided Design (ICCAD)* (pp. 1-9). IEEE.

Giron-Sierra, J. M. (2026). Multi-Objective Optimization. In *Introduction to Optimization with Matlab® Examples* (pp. 729-796). Cham: Springer Nature Switzerland.

Yadav, D., Ramu, P., & Deb, K. (2023, July). Finding robust solutions for many-objective optimization using NSGA-III. In *2023 IEEE Congress on Evolutionary Computation (CEC)* (pp. 1-8). IEEE.

Xu, Q., Xu, Z., & Ma, T. (2019, August). A short survey and challenges for multiobjective evolutionary algorithms based on decomposition. In *2019 International conference on computer, information and telecommunication systems (CITS)* (pp. 1-5). IEEE.

Zan, X., Wu, Z., Guo, C., & Yu, Z. (2020). A Pareto-based genetic algorithm for multi-objective scheduling of automated manufacturing systems. *Advances in Mechanical Engineering*, 12(1), 1687814019885294.

Pulivarthy, P., Kommineni, M., Aragani, V. M., & Rajashekaran, G. (2026). Real Time Data Pipeline Engineering for Scalable Insights. In *Machine Learning, Predictive Analytics, and Optimization in Complex Systems* (pp. 83-102). IGI Global Scientific Publishing.

Chen, W., Lin, B., Zhang, X., Lin, X., Zhao, H., Zhang, Q., & Kwok, J. T. (2025). Gradient-based multi-objective deep learning: Algorithms, theories, applications, and beyond. arXiv preprint arXiv:2501.10945.

Zhang, H., Ge, Y., Zhao, X., & Wang, J. (2025). Hierarchical deep reinforcement learning for multi-objective integrated circuit physical layout optimization with congestion-aware reward shaping. IEEE Access.

Schafer, B. C., & Wang, Z. (2019). High-level synthesis design space exploration: Past, present, and future. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 39(10), 2628-2639.

Tang, R., Ding, W., Ye, L., Wang, Y., & Zhou, H. (2019). Tradeoff analysis index for many-objective reservoir optimization. Water Resources Management, 33(13), 4637-4651.

Li, Z., Luo, H., Jiang, Y., Liu, H., Xu, L., Cao, K., ... & Liu, H. (2024). Comprehensive review and future prospects on chip-scale thermal management: Core of data center's thermal management. Applied Thermal Engineering, 251, 123612.

Chen, T. Y., Chuang, K., Hung, W., Lin, T. S., & Chen, Y. M. (2024, June). Package-System Thermal Modeling and New Material. In 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) (pp. 1-2). IEEE.

Yang, S., Ding, G., & Zeng, Z. (2025). Dynamic Capacity Optimization and Cost Reduction Strategies for Large-Scale Cloud Data Infrastructure. Computer Science Bulletin, 8(01), 290-309.

Safari, S., Khdr, H., Gohari-Nazari, P., Ansari, M., Hessabi, S., & Henkel, J. (2021). TherMa-MiCs: Thermal-aware scheduling for fault-tolerant mixed-criticality systems. IEEE Transactions on Parallel and Distributed Systems, 33(7), 1678-1694.